类别

2022年11月3日,国际半导体产业协会(SEMI)宣布成立全球半导体气候联盟(SCC),目前已有超过60家跨半导体价值链创始企业会员共同响应参与,希望透过贯彻联盟宗旨、加速产业生态圈减少温室气体排放的脚步。SEMI是一家服务于全球电子制造和设计供应链的行业协会,它由60多家半导体创始成员公司建立。SEMI国际标准部高级总监James Amano告诉《国际电子商情》姊妹平台EE Times,近年来,可持续发展已成为行业和SEMI 2,500名成员关注的焦点。尽管许多成员都有自己的可持续发展倡议,但SCC关注的是所有成员的声音,而不局限于个人的声音。Amano介绍说,SCC项目由SEMI成员公司在2021年联合启动,SCC关注非气候相关的环境、社会和治理(ESG)问题。具体来看,SCC包含三个关键点:协作、透明度和目标。SCC将帮助成员企业在共同的方法、技术创新和沟通渠道上进行合作,以持续减少温室气体的排放。SCC的透明度以每年公开报告进展的形式来体现,包括了公开企业范围1(Scope 1)、范围2(Scope 2)和范围3(Scope 3)的排放报告数据。Amano指出,他们的目标是制定短期和长期的脱碳目标,到2050年达到净零碳排放。SCC所有的创始成员都支持《巴黎协定》,并推动实现1.5℃目标导向转型路径的相关协定。“我们的根本目的是改善和减少半导体行业的二氧化碳排放。”他补充说。在不同的成员公司看来,SCC目标的实现具备不同的意义。比如,对于晶圆厂而言,提倡SCC可助力其达到节能目标。另外,可持续发展也会影响材料的种类和来源,因为其核心问题还是温室气体的排放。SCC将致力于帮助组织的成员解决范围1排放。范围1排放为直接排放,即企业直接控制的燃料燃烧活动和物理化学生产过程产生的直接温室气体排放;范围2的排放为间接排放,是企业外购能源产生的温室气体排放,包括电力、热力、蒸汽和冷气等;范围3的排放则为价值链上下游各项活动的间接排放,覆盖上下游范围广泛的活动类型。Amano认为,范围3排放是大部分供应链最大的挑战。范围3排放的来源多种多样,比如材料的生产和运输、废物处理、员工通勤以及公司自有车辆的使用等,它被认为是未来可持续发展的关键问题之一。他还表示,SCC将寻求与其他协会、非政府组织以及投资界合作。“我们需要大家全部参与进来,这将推动整个价值链向前发展。SCC的协作性质将意味着所有参与者都能从共享的情报和实践中受益。”美光科技等SCC创始成员公司已经加大了对可持续发展的关注,美光每年都会发布一份关于其ESG优先事项里程碑的进展报告。除了美光之外,应用材料也发布了年度可持续发展报告。Amano透露,专注可持续发展的公司在过去十年里累积的减排已取得进展。施耐德电气也SCC的创始成员公司,它非常注重整个生态系统的可持续性。最近在加拿大多伦多举行的基础设施/结构会议上,施耐德电气战略计划总监Carsten Baumann表示,可持续发展不再是“美好的拥有”,而是将更多转变为“必须拥有”。由于目前供应链面临的挑战,长期的可持续发展必须要解决供应商生态系统的复杂性,并注重透明度。施耐德发布了一个季度记分卡(2021-2025施耐德电气可持续发展影响指数(SSI)计划),作为公司可持续发展承诺的一部分,施耐德还列出了从电子材料到水、电的使用,包括整个制造业的使用情况。毕马威(KMPG)的研究表明,企业正采取实际行动来衡量和减少对环境不利影响。该研究还显示,可持续的商业实践越来越被视为企业义务,成为了整个ESG战略的一部分。责编:Clover.li

在经历缺芯危机之后,供应链设计的重要地位日益凸显。近日,《国际电子商情》姊妹平台EPSNews的主编Barbara Jorgensen,针对半导体行业的供应链设计做了简要分析。电子产品设计师和采购部门之间一直存在着一场拉锯战。工程师设计产品优先考虑的是能否实现最佳功能,而采购团队通常更关注组件的价格和交货日期。因此,工程师设计出采购部门认为无法制造的产品的情况其实并不少见。企业观念已经改变近年来的半导体短缺危机改变了这一切,零部件的可用性已成为企业考虑的优先事项,这促使更多原始设备制造商(OEM)做新产品的供应链设计(Design for Supply Chain,DFSC)。在新产品的开发过程中,工程师和采购团队不仅要考虑零部件的价格和性能,还要考虑替代器件、双重采购和供应商寿命等问题。Pure Storage是全闪存存储硬件和软件解决方案制造商,对新产品设计的频繁评审和跨职能团队合作是该公司DFSC流程的基础。Pure Storage负责运营的副总裁Mike Fitzgerald表示:“我们的供应链设计把灵活性放在优先考量的位置,这主要是为了提高供应链的透明度以及设立期望值。”据了解,该公司的DFSC实践基于52周以上的生命周期。当一个新产品接近发布时,DFSC属性的里程碑评审周期就会增加。而新产品一旦被开发出来,它的供应链就绪审查就会评估该产品的物料清单(Bill of Material,简称BOM)。对此,Fitzgerald透露说:“我们首先会查看哪些零部件可以双重采购,以及这些零部件在BOM清单上所占的百分比。我们有一种红色、黄色、绿色的零部件采购方式,通过这个方法我们能掌握所有零部件的信息,包括哪些零部件的交期是8周或12周等等。”因技术原因而采用单一采购来源的组件比双重采购来源的组件具有更高的风险管理水平。OEM通常与单一采购来源的供应商密切合作,后者与其战略客户共享技术路线图和生产计划表。当然,对于可双重采购且具有最小交货时间的部件也要进行评估,其中包括电容、电阻和其他IP&E(Interconnect, Passive, and Electromechanical,互连、无源和机电)设备等。Fitzgerald解释说:“为了能给设计团队实时反馈设备状况信息,我们需要深入研究每一个组件类别,在设备出现问题时帮助设计团队及时采取适当行动。”例如,BOM清单上某个部件的交付周期为40周,该部件的替代器件交付周期显示为8周。Fitzgerald表示,虽然公司一直在寻找性能最好的部件,但是对于工业标准件部件而言,40周的交付周期可能会导致项目延误。通常在这种情况下,Pure Storage会进行4次正式的产品评审,针对每个流程中的团队都会进行评审。提前做好供应链准备供应链专家强调,分销商通常与没有供应链经验的客户打交道,新产品开发过程中应尽早做出采购决策。安富利负责销售支持和供应商开发的副总裁Peggy Carrieres指出:“从采购团队的角度来看,客户‘拥有’的设计所需组件的交货周期可能过长。而那些可以双重采购的产品,使用无需重新设计电路板的架构,以及高EOL(End-of-life,项目终止/停产)风险的组件,尽早计划能提高它的制造和器件采购的成功率。”据介绍,Pure Storage有一个专门负责新产品采购的团队,该团队负责材料控制直到项目过渡到常态采购团队。新产品采购团队直接与公司的合同制造商(CM)合作,在发现故障时采取纠正措施,以确保物料的正常流动。Fitzgerald解释说:“新产品采购团队非常注重风险管理。当我们推出一款新产品时,他们就会建立一个将产品转入稳定状态的流程。”一般在产品发布6周后,新产品采购团队就会开发出强大的供应链模型,该模型确定了风险的范围,并采取了相应的措施来降低风险。随后,常态采购团队获得所有权,与工厂一起推动整个项目。Fitzgerald补充道:"如果在这个过程中发现了问题,我们也会让负责合约的商品团队参与进来,再由常态采购团队推动整个项目从供应到执行。”给予供应链最大的灵活性Fitzgerald把“模块化设计”称为“可延迟性设计(DFP)”,它为OEM的供应链提供了更高的灵活性,DFP在元器件交货时间可能长达60周的现在派上了用场。从供应链的角度来看,模块化设计降低了预测的复杂性,并能把库存数量降至最低。OEM和EMS供应商努力保持最低库存——不过,维持库存需要资金成本,随着时间的推移维持库存所带来的价值可能会下降。Fitzgerald说:“我们希望能保证订单在规定时间内交付。因此,在交付产品前的最后24-48小时内,客户就能够进入并配置订单。”最近,一项针对安富利客户的调查显示:EMEA(欧洲、中东、非洲)地区23%的受访者愿意推迟产品的发布日期,以克服半导体元元器件短缺带来的问题。在实际的产品设计过程中,25%的公司与多家制造商使用已获批准的零部件,而23%的公司在设计的早期就对零部件进行了测试和确认。“我认为,经历了过去几年的缺芯危机之后,半导体市场出现颠覆,会是一个新常态。”Carrieres总结道。文章翻译自《国际电子商情》姐妹刊EPSNews,原文链接:Why Design for Supply Chain is Gaining Ground责编:Clover.li

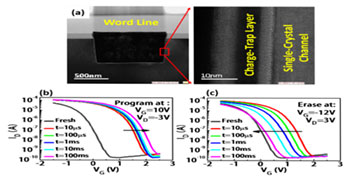

国际电子商情21日从中科院官网获悉,日前微电子所集成电路先导工艺研发中心研发团队研制出了一种高性能单晶硅沟道3D NOR储存器。NOR闪存以速度快、可靠性高和使用寿命长等优势,在人工智能、汽车电子和工业领域中发挥着不可替代的作用。目前普遍使用的平面NOR闪存在50纳米以下技术代的尺寸微缩遇到瓶颈,难以进一步提升集成密度、优化器件性能和降低制造成本。为突破上述瓶颈,研究人员提出了多种基于多晶硅沟道的三维NOR(3D NOR)器件,但多晶硅沟道迁移率低、读取速度慢,影响了NOR器件整体性能。单晶硅沟道3D NOR器件及电性实验结果:(a)器件TEM截图(左)及沟道局部放大图(右),(b)编程特性和(c)擦除特性 图源: IEEE Electron Device Letters据中科院介绍,微电子所研发团队使用研发的垂直晶体管新工艺制备出单晶硅沟道3D NOR三维阵列,其上下叠置的晶体管既具单晶硅沟道的高性能优势,又有三维一体集成的制造成本低的优点,可在获得同等或优于单晶硅沟道平面NOR闪存器件性能的同时,无需升级光刻机也可大幅提高存储器集成密度、增加存储容量。团队研制的3x3x2三维NOR闪存阵列实现了正常读写和擦除,达到了读电流以及编程、擦除速度与二维NOR闪存器件相当的目标,且新制程与主流硅基工艺兼容,便于应用。 责编:Elaine